# International Journal of Microwave and Wireless **Technologies**

cambridge.org/mrf

## **Research Paper**

Cite this article: Tsitsos SP, Giannenas IC (2024) Compact three-way planar power divider with a simple structure. International Journal of Microwave and Wireless Technologies 16(1), 69-74. https://doi.org/ 10.1017/S1759078723001046

Received: 11 December 2022 Revised: 19 August 2023 Accepted: 22 August 2023

**Keywords:**

planar; power divider; three way

Corresponding author: Stelios P. Tsitsos;

Email: s.tsitsos@ict.ihu.gr

© The Author(s), 2023. Published by Cambridge University Press in association with the European Microwave Association. This is an Open Access article, distributed under the terms of the Creative Commons Attribution licence (http://creativecommons. org/licenses/by/4.0), which permits unrestricted re-use, distribution and reproduction, provided the original article is properly cited.

# Compact three-way planar power divider with a simple structure

Stelios P. Tsitsos n and Ioannis C. Giannenas

Department of Information, Computer, and Telecommunications Engineering, International Hellenic University, Serres, Greece

#### **Abstract**

A simple and compact three-way planar power divider, which avoids the floating common node of the isolation resistors, is presented. The proposed structure exhibits a wideband operation (measured frequency range of 1.6-3.3 GHz and bandwidth of 69.4%) with good return loss and isolation characteristics. Transmission line theory is used for the mathematical analysis and extraction of design equations, followed by simulations and experimental measurements that confirm the predicted results. The proposed divider achieves an equal power split ( $\sim$ 32%,  $-4.9 \pm 0.4$  dB insertion loss) between the input and each output port. The measured return loss is better than -10 dB at all ports, and the measured maximum isolation is close to -30 dB. The proposed design exhibits a fully planar structure, thus eliminating the need for a floating common node for the isolation resistors. Additionally, its structure is much simpler (i.e., no coupled lines, crossovers, or lumped capacitors are required) than other designs, achieves wideband operation, and provides design simplicity, flexibility, and easy implementation. Despite its simple noncomplicated structure, the proposed three-way planar divider achieves similar (or in some cases, better) performance and size than other more complicated structures. Furthermore, it can be expanded to an *n*-way structure.

#### Introduction

Multi-way power dividers are key components in many microwave applications such as power and low-noise amplifiers as well as phased antenna arrays [1-3]. In recent years, there has been an increasing demand for low-cost, compact, and miniaturized power dividers for various microwave and mm-wave applications. For this purpose, Wilkinson-type [4] and Gysel-type dividers [5] are widely used. Generally, an *n*-way Wilkinson divider is nonplanar for n > 3because the 3D floating common node makes its planar implementation difficult. Although several planar structures have been proposed, they are rather complicated since they employ multi-section lines [6], p-i-n diodes [7], a multilayer structure [8], and coupled lines [9, 10]. Miniaturized planar structures have also been proposed, but they are also complicated because they either employ cascaded Lange couplers [11] or multi-section lines [12]. Recently, highisolation planar dividers based on a recombinant structure and multi-section impedance transformers have been presented [13, 14]. In [15], a very simple wideband planar structure with good return loss and isolation characteristics was proposed. However, this structure was analyzed using only  $\lambda/4$  lines, resulting in a  $3\lambda/4$ -long structure. More recent planar structures have been reported, but they are rather complicated since they employ composite right- and left-handed transmission lines with lumped capacitors [16] or provide only two-way power division [17].

In this work, we extend the work presented in [15] by investigating the design of a simple, wideband, and compact planar power divider with an arbitrary line length. It is demonstrated that the proposed structure can sufficiently operate using  $\lambda/8$  lines, resulting in an overall length of  $3\lambda/8$ , which is half of that reported in [15]. The proposed design achieves a wideband operation (1.6–3.3 GHz) and can be expanded to an *n*-way structure. It also uses practical characteristic impedance values (thus providing easy implementation) and offers design flexibility. The proposed planar divider is first theoretically analyzed using transmission line theory and then fabricated on a microstrip substrate. Finally, experimental measurements are performed to validate the theoretically predicted results.

### Circuit analysis

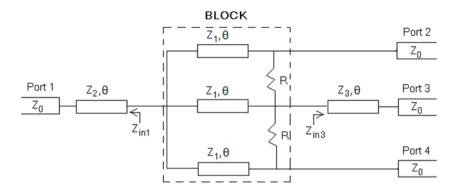

The proposed three-way planar power divider is presented in Fig. 1. It features a main block (shown as BLOCK), which consists of three transmission lines (each with characteristic impedance  $Z_1$ ). All lines have an arbitrary electrical length  $\theta$  (0°  $\leq \theta \leq 90$ °)

**Figure 1.** The proposed three-way wideband planar power divider employing transmission lines of arbitrary length  $\theta$ .

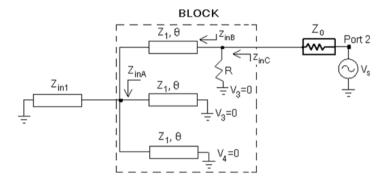

**Figure 2.** The circuit derived from the BLOCK (shown in Figure 1) by applying a voltage at port 2.

at the midpoint frequency of operation. The divider also employs two isolation resistors (each with value *R*) placed between ports 2 and 3 and between ports 3 and 4, respectively.

The extra transmission lines with characteristic impedances  $Z_2$  and  $Z_3$  and length  $\theta$  at the input (port 1) and output (port 3), respectively, achieve the wideband characteristics of the proposed power divider. In this work, we set  $\theta=45^\circ$  to achieve a compact design. If we increase  $\theta \tau o 90^\circ$ , the bandwidth will be increased but not significantly. However, this increase in  $\theta$  leads to an increase in the total length of the divider, as reported in [15]. On the other hand, if we make  $\theta<45^\circ$  to achieve a more compact design, the bandwidth will be decreased to some extent and the lines will become very short, leading to coupling effects and difficulties in implementation.

Equal power splitting is achieved by employing transmission lines with the same characteristic impedance  $Z_1$  inside the BLOCK (Fig. 1). The input and output lines with characteristic impedances  $Z_2$  and  $Z_3$ , respectively, also achieve impedance matching. The derived equations for the input impedances  $Z_{\rm inC}$  and  $Z'_{\rm inC}$  (see Fig. 1) are set equal to  $Z_0$  and  $Z_{\rm in3}$ , respectively, by imposing the matching condition at ports 2 and 3, as shown in equations (9) and (16).

The input impedances  $Z_{in1}$  and  $Z_{in3}$  are given as follows:

$$Z_{\text{in1}} = Z_2 \frac{Z_0 + jZ_2 \tan \theta}{Z_2 + iZ_0 \tan \theta},$$

(1)

$$Z_{\text{in}3} = Z_3 \frac{Z_0 + jZ_3 \tan \theta}{Z_3 + jZ_0 \tan \theta}.$$

(2)

Considering the components contained in the BLOCK (see Fig. 1), we initially apply a voltage source to port 2. Assuming ideal isolation at the remaining output ports, the voltages at ports 3 and 4 must be zero (i.e.,  $V_3 = V_4 = 0$ ). Therefore, from the BLOCK shown in Fig. 1, the circuit shown in Fig. 2 can be derived.

Based on Fig. 2,  $Z_{\text{in}A}$  can be calculated as follows:  $\frac{1}{Z_{\text{in}A}} = \frac{1}{Z_{\text{in}1}} + \frac{1}{jZ_1 \tan \theta} + \frac{1}{jZ_1 \tan \theta},$

which results in the following equation:

$$Z_{\text{in}A} = \frac{Z_{\text{in}1} \cdot jZ_1 \tan \theta}{jZ_1 \tan \theta + 2Z_{\text{in}1}}.$$

(3)

In equation (3), by substituting  $Z_{\text{in}1}$  from equation (1), the following equation can be obtained:

$$Z_{\text{in}A} = \frac{jZ_0Z_1Z_2 \tan \theta - Z_1Z_2^2 \tan^2 \theta}{jZ_1Z_2 \tan \theta - Z_0Z_1 \tan^2 \theta + 2Z_0Z_2 + j2Z_2^2 \tan \theta}.$$

(4)

Also, based on Fig. 2, the input impedance  $Z_{\mathrm{in}B}$  can be written as follows:

$$Z_{\text{in}B} = Z_1 \frac{Z_{\text{in}A} + jZ_1 \tan \theta}{Z_1 + jZ_{\text{in}A} \tan \theta}.$$

(5)

In equation (5), by substituting  $Z_{\text{in}A}$  from equation (4), the following equation can be obtained:

$$Z_{\text{in}B} = \frac{jZ_{\text{in}1}Z_1 \tan \theta - Z_1^2 \tan^2 \theta + j2Z_1Z_{\text{in}1} \tan \theta}{jZ_1 \tan \theta + 2Z_{\text{in}1} - Z_{\text{in}1} \tan^2 \theta}.$$

(6)

Furthermore, based on Fig. 2, the input impedance  $Z_{\rm inC}$  can be written as follows:

$$Z_{\text{inC}} = \frac{R \cdot Z_{\text{in}B}}{R + Z_{\text{in}B}}.$$

(7)

In equation (7), by substituting  $Z_{inB}$  from equation (6), the following equation can be obtained:

$$Z_{inC} = \frac{R \left[ j3Z_1 Z_2 \tan \theta \cdot \frac{Z_0 + jZ_2 \tan \theta}{Z_2 + jZ_0 \tan \theta} - Z_1^2 \tan^2 \theta \right]}{R \left[ jZ_1 \tan \theta + Z_2 \frac{Z_0 + jZ_2 \tan \theta}{Z_2 + jZ_0 \tan \theta} \cdot (2 - \tan^2 \theta) \right]} + \left[ j3Z_1 Z_2 \tan \theta \frac{Z_0 + jZ_2 \tan \theta}{Z_2 + jZ_0 \tan \theta} - Z_1^2 \tan^2 \theta \right]}.$$

(8)

**Table 1.** Electrical parameter values for the proposed power divider in Figure 1

| $Z_0$ (Ohm) | Z <sub>1</sub> (Ohm) | $\theta$ (degrees) | R (Ohm) | Z <sub>2</sub> (Ohm) | Z <sub>3</sub> (Ohm) |

|-------------|----------------------|--------------------|---------|----------------------|----------------------|

| 50          | 90                   | 45                 | 100     | 23.23                | 47.91                |

The above equation can also be derived if a voltage source is applied to port 4 because the divider of Fig. 1 is symmetric along its central axis.

The matching condition at port 2 requires

$$Z_{\rm inC} = Z_0. \tag{9}$$

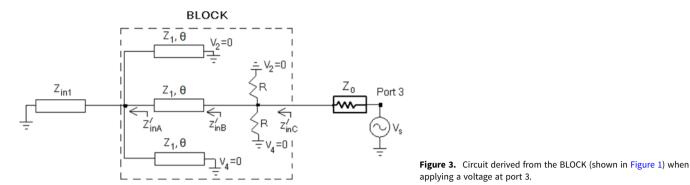

Next, we apply a voltage source to port 3. Assuming ideal isolation at the remaining output ports, the voltages at ports 2 and 4 must be zero (i.e.,  $V_2=V_4=0$ ). Therefore, from the BLOCK shown in Fig. 1, the circuit shown in Fig. 3 can be derived.

Based on Fig. 3,  $Z'_{inA}$  can be calculated as follows:

$$\frac{1}{Z'_{\mathrm{in}A}} = \frac{1}{Z_{\mathrm{in}1}} + \frac{1}{jZ_1 \tan \theta} + \frac{1}{jZ_1 \tan \theta},$$

which results in the following equation:

$$Z'_{\text{in}A} = \frac{Z_{\text{in}1} \cdot jZ_1 \tan \theta}{jZ_1 \tan \theta + 2Z_{\text{in}1}}$$

(10)

In equation (10), by substituting  $Z_{\rm in1}$  from equation (1), the following equation can be obtained:

$$Z'_{\text{in}A} = \frac{jZ_1Z_2 \, \tan\theta \cdot (Z_0 + jZ_2 \, \tan\theta)}{jZ_1 \, \tan\theta \cdot (Z_2 + jZ_0 \, \tan\theta) + 2Z_2 \cdot (Z_0 + jZ_2 \, \tan\theta)}. \tag{11}$$

Also, based on Fig. 3, the input impedance  $Z'_{\mathrm{in}B}$  can be written as follows:

$$Z'_{\text{in}B} = Z_1 \frac{Z'_{\text{in}A} + jZ_1 \tan \theta}{Z_1 + jZ'_{\text{in}A} \tan \theta}.$$

(12)

In equation (12), by substituting  $Z'_{\text{in}A}$  from equation (10), the following equation can be obtained:

$$Z_{\text{in}B}' = Z_1 \frac{-3Z_1Z_2^2\tan^2\theta - {Z_1}^2Z_2\tan^2\theta + jZ_0Z_1Z_2\tan\theta}{-jZ_0Z_1^2\tan^3\theta + j2Z_0Z_1Z_2\tan\theta} \\ -Z_0Z_1^2\tan^3\theta + j2Z_0Z_1Z_2\tan\theta \\ -Z_0Z_1^2\tan^2\theta + 2Z_0Z_1Z_2 - Z_0Z_1Z_2\tan^2\theta \\ +jZ_1^2Z_2\tan\theta + j2Z_1Z_2^2\tan\theta - jZ_1Z_2^2\tan^3\theta \end{aligned}.$$

Furthermore, based on Fig. 3, the input impedance  $Z'_{\text{in}C}$  can be written as follows:

$$Z'_{\text{in}C} = \frac{RZ'_{\text{in}B}}{R + 2Z'_{\text{in}B}}.$$

(14)

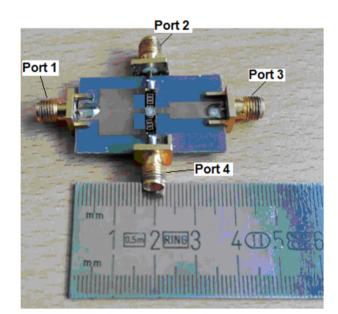

Figure 4. Fabricated PCB of the proposed power divider.

In equation (14), by substituting  $Z'_{inB}$  from equation (12), the following equation can be obtained:

$$Z'_{\text{inC}} = \frac{RZ_1 \left( -3Z_1Z_2^2 \tan^2 \theta - Z_1^2 Z_2 \tan^2 \theta + jZ_0 Z_1 Z_2 \tan \theta \right)}{-jZ_0Z_1^2 \tan^3 \theta + j2Z_0Z_1Z_2 \tan \theta}$$

$$\frac{-jZ_0Z_1^2 \tan^3 \theta + j2Z_0Z_1Z_2 - Z_0Z_1Z_2 \tan \theta}{+jZ_1^2 Z_2 \tan \theta + j2Z_1Z_2^2 \tan \theta - jZ_1Z_2^2 \tan^3 \theta}$$

$$+2Z_1 \left( -3Z_1Z_2^2 \tan^2 \theta - Z_1^2 Z_2 \tan^2 \theta + jZ_0Z_1Z_2 \tan \theta - jZ_0Z_1^2 \tan^3 \theta + j2Z_0Z_1Z_2 \tan \theta \right). \tag{15}$$

The matching condition at port 2 requires

$$Z'_{\rm inC} = Z_{\rm in3}.\tag{16}$$

## Implementation, results, and discussion

Equations (8), (9) and (15), (16) can be used as the design equations of the proposed power divider. These equations are satisfied for a number of solutions. Thus, the variety of parameter values provides design flexibility. To achieve a compact design,  $\theta = 45^{\circ}$  was selected at a midpoint frequency of 3 GHz. Also, by selecting  $Z_0 = 50$  Ohm, R = 100 Ohm, and  $Z_1 = 90$  Ohm,

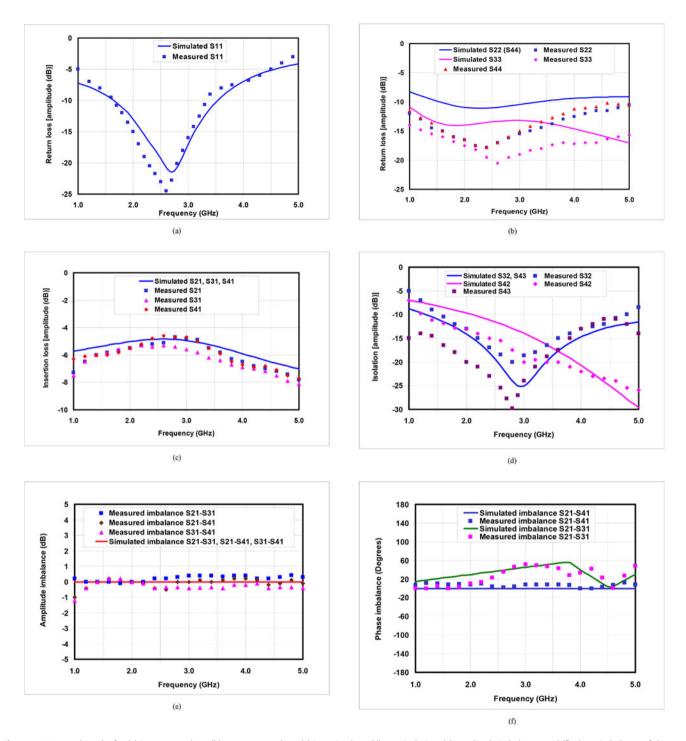

Figure 5. Measured results for (a) input return loss, (b) output return loss, (c) insertion loss, (d) port isolation, (e) amplitude imbalance, and (f) phase imbalance of the proposed three-way planar divider shown in Figure 1

equations (8), (9) and (15), (16) yield practically realizable impedance values ( $Z_2 = 23.23$  Ohm and  $Z_3 = 47.91$  Ohm). These parameter values are summarized in Table 1.

The proposed three-way wideband planar power divider shown in Fig. 1 was fabricated on a printed circuit board (PCB) using a TACONIC substrate with a typical dielectric constant of 2.2 (Fig. 4). The layout of the proposed power divider was produced using the Advanced Design System simulation software. Then, we placed a mask of the layout on the top copper surface of the

TACONIC substrate and immersed it into a solution of sodium hydroxide to remove the unwanted copper. Thus, the upper conductors of the microstrip lines with the desired dimensions were fabricated. Commercial 100-Ohm resistors were used to achieve the necessary isolation between the output ports. These resistors could, in principle, cause some parasitic effects. However, in the operating frequency range of the divider, these effects are negligible. We employed an Agilent E5071C vector network analyzer to measure the scattering parameters (amplitude and phase) of the

Table 2. Performance comparison of the proposed structure with the performance of previously published works

| Ref.      | Design structure                                                                                                                   | Return loss (dB)                        | Insertion loss (dB)         | Max. isolation (dB)              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------|----------------------------------|

| [8]       | Three-way, narrow-coupled lines, slotted ground plane, lumped capacitors                                                           | <-16                                    | -4.77                       | -17                              |

| [9]       | Three-way, narrow-coupled lines                                                                                                    | <-10                                    | -4.80                       | -19                              |

| [11]      | Three-way, inner-layer crossovers, Lange couplers (operation at $<$ 0.8 GHz)                                                       | <-20                                    | -5.10                       | -35                              |

| [13]      | Three-way planar                                                                                                                   | <-10                                    | -4.99                       | -30                              |

| [14]      | Three-way planar                                                                                                                   | <-10                                    | -4.99                       | -31                              |

| [15]      | Three-way planar                                                                                                                   | <-13                                    | -4.60                       | -20                              |

| [16]      | Eight-way planar, composite right- and left-handed transmission line, hybrid coplanar waveguide microstrip line, lumped capacitors | <-15                                    | -9.20                       | -40                              |

| [17]      | Two-way planar                                                                                                                     | <-11                                    | -3.00                       | -15                              |

| This work | Three-way planar                                                                                                                   | <-10                                    | -4.90                       | -30                              |

| Ref.      | Maximum amplitude imbalance (dB)                                                                                                   | Maximum phase<br>imbalance<br>(degrees) | Fractional<br>bandwidth (%) | Overall size                     |

| [8]       | 2.00                                                                                                                               | Not mentioned                           | 97.8                        | $0.86\lambda \times 0.86\lambda$ |

| [9]       | 0.20                                                                                                                               | Not mentioned                           | 96.0                        | $0.59\lambda \times 0.38\lambda$ |

| [11]      | 1.20                                                                                                                               | 90                                      | 42.7                        | $0.54\lambda \times 0.10\lambda$ |

| [13]      | 2.00                                                                                                                               | Not mentioned                           | 34.8                        | $0.26\lambda \times 0.31\lambda$ |

| [14]      | 2.00                                                                                                                               | 8                                       | 43.5                        | $0.27\lambda \times 0.34\lambda$ |

| [15]      | 0.40                                                                                                                               | Not mentioned                           | 66.7                        | $0.75\lambda \times 0.37\lambda$ |

| [16]      | 0.24                                                                                                                               | ~5                                      | 36.4                        | $0.25\lambda \times 0.27\lambda$ |

| [17]      | 0.50                                                                                                                               | Not mentioned                           | 52.6                        | $0.32\lambda \times 0.20\lambda$ |

| This work | 0.80                                                                                                                               | ∼51                                     | 69.4                        | $0.38\lambda \times 0.26\lambda$ |

fabricated PCB over the frequency range 1-5 GHz. Before conducting measurements, we performed the standard transmission line-through calibration procedure. The graphs in Fig. 5 show the simulated and experimental responses of the proposed divider. Good agreement can be observed. The discrepancies are mainly due to the limited accuracy of the etching process and the effect of the connectors, which were not included in the simulation. Due to our limited lab resources, we could not perform any calibration or correction procedures to address the discrepancies caused by the etching process and connectors during the measurement process. It is evident that in the frequency range 1.6–3.3 GHz (a fractional bandwidth of  $\frac{3.3-1.6}{2.45} \cong 69.4\%$ ), the proposed divider achieves equal power split ( $\sim 32\%$ ,  $-4.9 \pm 0.4$  dB insertion loss) between the input and each output port and good matching and isolation characteristics. The measured return loss is better than  $-10 \, \mathrm{dB}$  at all ports, and the measured maximum isolation is close to -30 dB. The maximum measured amplitude imbalance is  $\sim$ 0.8 dB. The maximum measured phase imbalance between ports 2 and 4 is  $\sim$ 8 degrees, whereas that between ports 2 and 3 (or 4 and 3) is  ${\sim}51$  degrees. This is due to the extra length  $\theta$  of the line with characteristic impedance  $Z_3$  shown in Fig. 1.

Generally, the phase imbalances measured are not significant in applications requiring an accurate splitting ratio. However, the phase imbalances measured between certain ports, although acceptable, may have an impact in phase array applications. In cases requiring very small phase imbalances, an appropriate phase shifter could be used.

A performance comparison of the proposed planar power divider with the performance of previously published designs is shown in Table 2. It is evident that the performance of the proposed design is better than the performance of most other designs in terms of insertion loss, isolation, bandwidth, and size but falls short in terms of return loss. However, its design flexibility, easy implementation, and expansion to an *n*-way structure make it an attractive proposition.

#### Conclusion

In this work, a planar three-way wideband power divider that avoids the floating common node of the isolation resistors was designed, simulated, fabricated, and tested. The mathematical analysis and extraction of design equations were based on the transmission line theory. The divider was fabricated on a microstrip substrate. Measured results showed a good agreement with the predicted data. It was also demonstrated that despite its very simple noncomplicated structure, the proposed design achieves similar performance and size compared with other more complicated structures. Furthermore, it provides design flexibility, can be easily implemented, and can be expanded to an *n*-way structure.

**Competing interests.** The authors declare no conflict of interests.

#### References

- Kumar OP, Ali T, Kumar P, Kumar P and Anguera J (2023) An ellipticalshaped dual-band UWB notch antenna for wireless applications. Applied Sciences 13, 1310.

- Kumar OP, Ali T and Kumar P (2023) A novel corner etched rectangular shaped ultrawideband antenna loaded with truncated ground plane for microwave imaging. Wireless Personal Communications 130, 2041–2259.

- Kumar OP, Kumar P, Ali T, Kumar P and Subhash BK (2023) A quadruple notch UWB antenna with decagonal radiator and Sierpinski square fractal slots. *Journal of Sensor and Actuator Networks* 12, 24.

- Choe W and Jeong J (2014) Compact modified Wilkinson power divider with physical output port isolation. *IEEE Microwave and Wireless Components Letters* 24(12), 845–847.

- Wu H, Wu Y, Yang Q, Wang W and Kishk AA (2020) Generalized highisolation n-way Gysel power divider with arbitrary power ratio and different real terminated impedances. *International Journal of RF and Microwave Computer-Aided Engineering* 30, e22016.

- Zhou J, Morris KA and Lancaster M (2007) General design of multiway multisection power dividers by interconnecting two-way dividers. *IEEE Transactions on Microwave Theory and Techniques* 55(10), 2218–2215.

- Fan H, Liang X, Geng J, Liu L and Jin R (2017) An n-way reconfigurable power divider. IEEE Transactions on Microwave Theory and Techniques 65(11), 4122–4137.

- 8. **Abbosh AM** (2006) Three-way parallel-coupled microstrip power divider with ultrawideband performance and equal-power outputs. *IEEE Microwave and Wireless Components Letters* **21**(12), 649–651.

- Chiu J-C, Lin J-M and Wang Y-H (2006) A novel planar three-way power divider. IEEE Microwave and Wireless Components Letters 16(8), 449–451

- 10. **Kim S, Jeon S and Jeong J** (2011) Compact two-way and four-way power dividers using multi-conductor coupled lines. *IEEE Microwave and Wireless Components Letters* **21**(3), 130–132.

- Hayashi H (2015) Miniaturized broadband three-way power divider. In IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO). Taiwan

- Zhang T, Che W and Chen H (2017) Miniaturized multiway unequal power divider with controllable characteristic impedances. *IEEE Microwave and Wireless Components Letters* 27(12), 1062–1064.

- Abdullah A, Farooq MA, Zakir MA and Cheema HM (2019) A novel, broadband, divide-by-3 planar power divider. In *IEEE Asia-Pacific Microwave Conference (APMC)*. Singapore.

- Abdullah A, Zakir MA and Cheema HM (2020) A divide-by-3 planar power divider with >30 dB isolation. *Microwave and Optical Technology* Letters 62(5), 1940–1944.

- Tsitsos S, Anastassiu H and Papatsoris A (2014) 3-way wide-band planar power divider. In 22nd Telecommunications Forum Telfor (TELFOR). Serbia

- Song K, Zhao P, Chen Y and Patience SR (2020) Compact high-isolation planar eight-way power divider using zero-phase isolation circuit. *IET Microwaves, Antennas & Propagation* 14(8), 774–778.

- Tadayon H, Ardakani MD, Karimian R, Ahmadi S and Zaghloul M (2022) A novel planar power divider/combiner for wideband, high-power applications. Eng 3, 467–475.

Stelios Tsitsos was born in Greece. He was awarded the Diploma in Electrical and Computer Engineering from the Democritus University of Thrace, Greece, and the M.Sc. in Communication Engineering and Digital Electronics from the Department of Electrical and Electronics Engineering, UMIST, UK. He was also awarded the Ph.D. Degree in Microwave Engineering from the same Department, where he also worked as

a Research Assistant and then as a Research Associate. Afterwards, he joined the Greek Telecoms Organisation as a Senior Telecommunications Engineer. He is currently a Professor in the Department of Information, Computer and Telecommunications Engineering, International Hellenic University, Serres Campus, Greece. His research interests include the design and characterization of microwave components and sub-systems for various telecommunication applications.

Ioannis Giannenas was born in Greece. He was awarded the B.Sc. Degree in Information and Communications Engineering from Epirus Technological and Educational Institute, Greece, and the M.Sc. in Telecommunications from the Department of Information, Computer and Telecommunications Engineering, International Hellenic University, Serres Campus, Greece. He is currently teaching courses in Informatics and

Communications to high-school students in Greece.